# **Almost Perfectly Symmetric SWCNT-Based CMOS Devices** and Scaling

Zhiyong Zhang, \*\* Sheng Wang, \*\* Zhenxing Wang, \*\* Li Ding, \*\* Tian Pei, \*\* Zhudong Hu, \*\* Xuelei Liang, \*\* Qing Chen, Tan Li, and Lian-Mao Pengt, and Lia

tkey Laboratory for the Physics and Chemistry of Nanodevices and Department of Electronics, Peking University, Beijing 100871, China, and Key Laboratory for the Physics and Chemistry of Nanodevices and College of Chemistry and Molecular Engineering, Peking University, Beijing 100871, China

omplementary metal-oxidesemiconductor (CMOS) is a major class of integrated circuits and shares over 75% market of the semiconductor industry due to its tremendous advantages of high noise immunity and low static power consumption. CMOS is also sometimes referred to as complementary symmetry metal-oxide-semiconductor (or COS-MOS) to emphasize the fact that typical digital circuitry design style uses complementary and symmetrical pairs of p-type (hole) and n-type (electron) MOS field-effect transistors (FETs) for logic functions.<sup>1</sup> Unfortunately, perfect symmetric CMOS has never been realized. This is because for all important semiconductors the band structures are intrinsically not symmetric around their band gaps or between the conduction and valence bands. Typically, electrons have a smaller effective mass than that of holes, and the performance of n-FETs is much better than that of p-FETs. As a result of this intrinsic asymmetric band structures of Si and all major semiconductor (including III-V and II-VI compounds) holes move much slower in MOS FET devices than electrons, 2,3 dragging the overall performance of the CMOS circuits. In this work, we will show, by using single-walled carbon nanotube (SWCNT) as the conduction channel material, that almost perfect symmetric CMOS devices and circuits can be realized. This is because the band structure of a semiconductor SWCNT is almost perfectly symmetric between its conduction and valence bands. A careful evaluation of a SWCNT-based CMOS inverter reveals that electron and hole mobilities of over 3000 cm<sup>2</sup>/V·s are realized simultaneous on the adjacent SWCNT-based n- and p-type FETs

ABSTRACT Symmetric n- and p-type field-effect transistors (FETs) have been fabricated on the same undoped single-walled carbon nanotube (SWCNT). The polarity of the FET is defined by controlled injection of electrons (ntype, via Sc electrodes) or holes (p-type, via Pd electrodes) into the SWCNT, instead of via chemically doping the SWCNT. The SWCNT-based FETs with different channel lengths show a clear trend of performance improvement for channel length scaling. Taking full advantage of the perfect symmetric band structure of the semiconductor SWCNT, a perfect SWCNT-based CMOS inverter is demonstrated, which gives a voltage gain of over 160, and for the two adjacent n- and p-type FETs fabricated on the same SWCNT, high field mobility is realized simultaneously for electrons (3000 cm<sup>2</sup>/V  $\cdot$  s) and holes (3300 cm<sup>2</sup>/V  $\cdot$  s).

**KEYWORDS:** carbon nanotube · CMOS · inverter · mobility · scaling

fabricated on the same SWCNT, leading to an almost perfect CMOS inverter with perfect logic high and low states, a voltage gain of over 160, and extremely low power dissipation.

The recent announcement by Intel company on the completion of its development of a 32 nm process<sup>4</sup> raises once again the concern that silicon-based CMOS is quickly approaching its end, and further improvements in transistor speed and performance will have to come from new materials rather than from scaling silicon further.<sup>5</sup> Several possibilities have been considered for beyond Si technology, in particular those based on III-V compounds and nanowires, graphene, and carbon nanotubes (CNTs).5 Indeed, extensive investigations have been carried out during the past decade on semiconducting CNTs for their potential use as the conduction channel material to replace Si.<sup>6-8</sup> Among other advantages, CNTs have a unique one-dimensional (1D) structure which leads to much reduced scattering and very high carrier mobility and sometimes even ballistic transport on devices of the length scale of less than 200 nm. A semiconductor CNT also has an almost perfect

\*Address correspondence to zyzhang@pku.edu.cn, Impeng@pku.edu.cn.

Received for review August 24, 2009 and accepted October 15, 2009.

Published online October 21, 2009. 10.1021/nn901079p CCC: \$40.75

© 2009 American Chemical Society

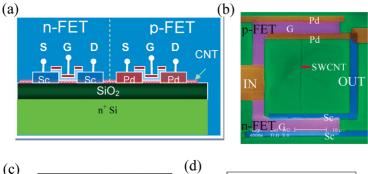

Figure 1. SWCNT-based CMOS FETs with self-aligned top gate. (a) Side view schematic of SWCNT CMOS devices with a pair of p- and n-FETs. (b) SEM image showing a SWCNT CMOS inverter which is composed of a p-FET (top) and a n-FET (bottom). The gate length for both FETs is 4  $\mu$ m. (c) Field transfer characteristics ( $I_{ds}-V_{gs}$ ) and (d) output characteristics ( $I_{ds}-V_{ds}$ ) of a pair of SWCNT CMOS FETs with gate length  $L_g=1.0~\mu$ m.

symmetric band structure between its conduction and valence bands<sup>9</sup> and consequently essentially the same effective mass for electrons and holes. This band structure symmetry may in principle lead to the same electron and hole mobilities and similar performance for nand p-type FETs which are necessary for perfect CMOS performance. Unfortunately, perfect symmetric CNTbased CMOS devices and integrated circuits (ICs) have not been realized, and this is largely due to the laggard developments on n-type devices. It has long been realized that the as-grown CNTs usually exhibit p-type field characteristics, and the performance of the p-type CNT FET was pushed almost to its limit in 2004 immediately after the discovery that Pd forms almost perfect ohmic contact with the CNT and can be used as the source (S)/ drain (D) electrodes for high-performance p-type CNT FETs. 10,11 Although a number of SWCNT-based CMOS devices and ICs have been fabricated, 12-16 the full advantage of the symmetric band structure of the CNT was not demonstrated adequately due to the cumbrance from n-type FETs. In an earlier paper, we demonstrated that Sc may be used to form almost perfect ohmic contact to the conduction band of the CNT,17 and the performance of n-type CNT FETs was pushed almost to their performance limit by combining the Sccontacted CNT FETs with a novel self-aligned metal gate with high-k gate dielectric. 18,19 The time is now ripe for developing perfect symmetric CNT-based CMOS technology.

Unlike conventional Si-based CMOS, where the polarity of the FETs is defined by doping the conduction channel of the device with suitable dopant atoms, in CNT-based CMOS, <sup>17,20</sup> the polarity of the FETs

can be defined by controlling the injection of carriers to the channel. While Pd may be used to inject holes barrier-free into the valence band of the CNT to form high-performance p-type FETs, 10,11 Sc may be used to inject electrons barrier-free into the conduction band of the CNT to form almost perfect n-type FETs.<sup>17–20</sup> This is a doping-free process. Both high-performance p- and n-type FETs can then be fabricated on the same intrinsic SWCNT, which may in principle lead to perfectly symmetric CMOS devices and circuits. Although symmetric n-type and p-type CNT FETs were fabricated with back-gate structure in our earlier works, 17,20 these back-gate devices cannot deliver near perfect performance due to the intrinsic limitation of the back-gate geometry. In this paper, we are concerned with the highefficient self-aligned top-gate geometry<sup>19</sup> that affords the almost perfect performance of the CNT FETs as demonstrated by the many examples given in this paper.

### **RESULTS AND DISCUSSION**

Figure 1a depicts a side view of the CNT-based CMOS device structure, and Figure 1b shows a top view scanning electron microscopy (SEM) image of a real CNT-based CMOS inverter, which we will discuss later. Current-voltage characteristics for a pair of typical p- and n-FETs fabricated on the same SWCNT with a diameter of 2 nm and a gate length of 1.0 µm are shown in Figure 1c,d. All electrical measurements were carried out in air using a probe station without intentionally protecting or packaging the devices. Figure 1c shows clearly that the Sccontacted CNT FET is n-type (blue curve) and the Pdcontacted CNT FET is p-type (red curve), and the field transfer characteristics are in many important aspects symmetric with each other. For example, the maximum ON/OFF current ratio  $I_{on}/I_{off}$  is larger than  $10^5$  at  $V_{ds} = 0.1$  V, and the subthreshold swing [SS =  $dV_{gs}/d(log I_{ds})]$  is about 90 mV/decade for the Pdcontacted p-type CNT FET, and the corresponding values for the Sc-contacted n-type CNT FET are 105 and 100 mV/decade, respectively. The linear  $I_{ds} - V_{ds}$ characteristics shown in Figure 1d indicate that ohmic contacts are formed for both p-type and n-type FETs at room temperature, and earlier studies showed that this behavior persists down to about 4.2 K.<sup>10,17</sup> The two sets of  $I_{ds} - V_{ds}$  curves for the p-type FET (red curve) and n-type FET (blue curve) are again similar for the whole range of values  $|V_{qs} - V_{th}|$  ( $V_{th}$  being the threshold voltage of the FET) from 0 to 1.0 V. To quantitatively assess the performance of both the n- and p-type CNT FETs, here we consider some key device parameters for a fixed supply voltage  $V_{\rm dd} = 1.0$  V. The first device param-

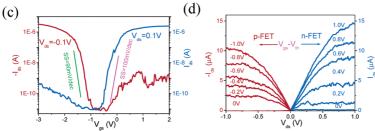

Figure 2. Comparison of seven device parameters between seven n-type and eight p-type CNT FETs, which are fabricated on the same SWCNT with a diameter of 2 nm. All of the parameters are plotted  $v_s$  gate length from 0.6 to 8  $\mu$ m. (a) Subthreshold swing SS. (b) Threshold voltage  $V_{th}$ . (c) ON-state conductance  $G_{on}$ . (d) Peak transconductance  $G_{m}$ . (e)  $I_{on}$  and  $I_{off}$  and (f) intrinsic gate delay. In all of these figures, red circles represent p-FETs and blue forks represent n-FETs. All of the parameters are calculated assuming the device operating under the bias of  $V_{tid} = 1.0 \text{ V}$ .

eter is the ON-state channel conductance (normalized by  $4e^2/h$ ),  $G_{on}$ , which is defined as  $G = dI_{ds}/dV_{ds}$ at low bias ( $V_{ds} = 0.1 \text{ V}$ ) and  $|V_{qs} - V_{th}| = 1 \text{ V}$ . The second device parameter is the peak transconductance,  $g_{\rm m}$ , which is defined as  $g_{\rm m}={\rm d}I_{\rm ds}/{\rm d}V_{\rm gs}$  and may be obtained from the  $I_{ds}-V_{qs}$  curves under the bias of  $|V_{ds}| = 1$  V. Other parameters include the ONand OFF-state currents, Ion and Ioff, which are determined by anchoring the  $V_{\rm qs}$  window around  $V_{\rm th}$  on the  $I_{ds} - V_{gs}$  curves at  $|V_{ds}| = 1$  V with  $V_{gs}$  swing at 0.67 V above  $V_{\rm th}$  for determining  $I_{\rm on}$  and 0.33 V below  $V_{\rm th}$ for determining Ioff. 21 Using the field transfer characteristics shown in Figure 1c, we obtain the ON-state conductance  $G_{\rm on}$  0.13 imes  $4e^2/h$  for the n-type FET and  $0.16 \times 4e^2/h$  for the p-type FET, and from Figure 1d, we obtain the corresponding  $g_{\rm m}=14.5~\mu{\rm S}$  for the n-FET and 17.0 µS for the p-FET. It is noted that

this is the first time that the  $g_{\rm m}$  value exceeds 10  $\mu$ S simultaneously for both the n-FET and p-FET fabricated on the same SWCNT.<sup>13–16</sup>

For IC applications, it is highly desirable to fabricate all of the devices with uniform performance. Fifteen transistors are fabricated on the same SWCNT with a diameter of 2 nm, as shown in Figure 1b, but the devices were fabricated with different gate lengths ranging from 8 to 0.6  $\mu m$  to explore the scaling behavior of CNT FETs. Among the 15 FETs, seven are p-type and eight are n-type. All 15 transistors have similar subthreshold swing SS ranging from 80 to 140 mV/decade, as shown in Figure 2a. The threshold voltages for all 15 FETs are shown in Figure 2b. These threshold voltages divide clearly into two groups; those between -0.8 and -1.4 V are associated with p-type CNT FETs, and those between -0.4 and 0.45 V are associated with

n-FETs. The separation of the threshold voltages  $V_{\rm th}$  between n- and p-type FETs is important to ensure that the p-FET and n-FET do not open simultaneously so that no direct path exists between the supply and ground rails under steady-state operating conditions and hence to lower power dissipation. Four additional device parameters ( $G_{on}$ ,  $g_{m}$ ,  $I_{on}$ , and  $I_{off}$ ) are calculated from experimental current-voltage characteristics to assess the electrical performance of these FETs, and these parameters are plotted *versus* gate length in Figure 2c-e. These figures show clearly that the n-type and p-type FETs of the same gate length exhibit very similar behavior, resulting in very similar values for all four important device parameters. Toward shorter gate length and in particular for  $I_{\text{off}}$ , the device parameter shows noticeable fluctuations. These fluctuations might result from contaminations or defects in the SWCNT channel, at the SWCNT/metal electrode interface,<sup>22</sup> or from the inhomogeneous HfO<sub>2</sub> gate dielectric. In principle, we can minimize or sometimes even eliminate some systematic performance fluctuations among devices through optimizing the process in the further. The leakage current  $I_{\text{off}}$  is a key parameter which reflects the standby power consumption of the device. For all devices examined here (Figure 2e),  $I_{\rm off}$  is smaller than  $1 \times 10^{-7}$  A and typical at the level of tens of nA when the device operates at  $V_{\rm DD}=1$  V.

Three important device parameters,  $G_{on}$ ,  $g_{m}$ , and  $I_{on}$ , show clear trend on the gate length scaling, suggesting that we can improve the performance of the SWCNT-based CMOS devices and integrated circuits by shrinking the gate length similar to the scaling as used in semiconductor industry in the past four decades; that is, the SWCNT-based CMOS devices are scalable. Figure 2c shows that  $G_{\rm on}$  will exceed 0.1  $\times$  4 $e^2/h$ , and Figure 2d shows that  $g_{\rm m}$  will become larger than 10  $\mu$ S for both the p- and n-type devices when gate length becomes smaller than 2  $\mu$ m. When normalized by d (d is the diameter of the SWCNT and represents the channel width), the values of  $q_{\rm m}$  become more than 5000  $\mu$ S/ $\mu$ m for both n- and p-FETs with a gate length shorter than 2.0 µm, and these values should be compared to the most recent values of about 2000  $\mu$ S/ $\mu$ m for p-FETs and 2200 μS/μm for n-FET announced by Intel for its 32 nm process.4

It is well-known that electron has smaller effective mass than a hole in silicon due to its asymmetric band structures.<sup>23</sup> Consequently, the electron mobility is about two times larger than that of the hole in silicon, and the performance of n-FETs is much better than that of the p-FETs with the same gate length and width. Although the dc characteristics of the p-FET can be improved to match the n-FET through enlarging the channel width 2–3 times that of the n-type FET, the switching speed of the p-FET cannot be made as good as that of the n-FET. As a result, the speed of Si CMOS circuit is dragged by the p-FET. This problem does not

exist in CNT-based CMOS technology. This is because, in CNT, the conduction band and valence band are symmetric about the band gap of the CNT.9 In CNT-based CMOS technology, n- and p-type devices are intrinsically symmetric, leading to symmetric performance not only on dc characteristics but also on switching speed. Here we use the intrinsic gate delay as the performance metric to describe the intrinsic switching speed of the transistors. The gate delay is defined as  $CV_{ds}/I_{on}$ , in which C is the total gate capacitance.<sup>21</sup> All CNT-based FETs discussed in this paper are fabricated on the same SWCNT with a diameter of d = 2.0 nm, which is covered on top by a gate dielectric HfO2 thin film with a thickness t = 15 nm and  $\varepsilon_r = 15$ . The gate capacitance for this top gate device geometry is estimated to be C =1.5 pF/cm. The gate delay values versus gate length for all 15 n-type and p-type CNT FETs are depicted in Figure 2f. This figure shows beautifully that the n-FET and p-FET with the same gate length have almost identical gate delay, and this delay exhibits again a clear decreasing trend as the gate length decreases. It is thus demonstrated that an almost perfect match has been realized for CNT-based CMOS devices not only for their dc performance via symmetry in, for example, G<sub>ON</sub>, which can also be realized in Si-based CMOS by varying the width of the device, but also in dynamical operation via gate delay, and this is not an easy thing to do in the Sibased CMOS process.

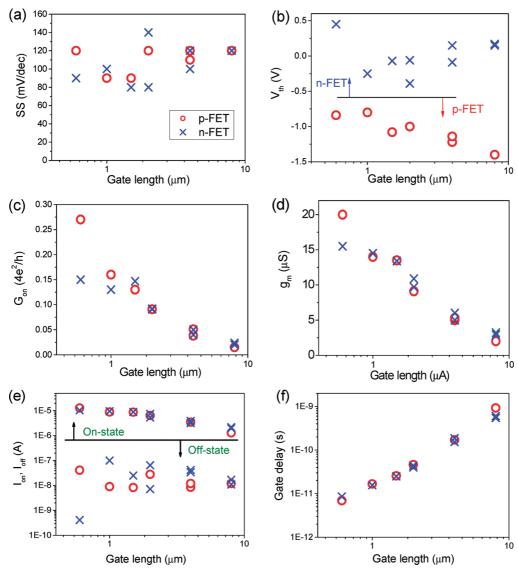

A CMOS inverter is the simplest and perfect CMOS circuit for illustrating the advantages of CMOS circuits. Figure 1b shows a top view SEM image of a CNT-based CMOS inverter. This inverter is composed of a pair of adjacent n- and p-type FETs fabricated on the same SWCNT with d=2 nm and the same gate length of  $L_{\rm g}=4.0~\mu{\rm m}$ . The field transfer (Figure 3a) and output characteristics (Figure 3b) are almost perfectly symmetric between the n- and p-type FETs. The field-dependent mobility for both electrons (n-type) and holes (p-type) can be calculated from the transfer characteristics (Figure 3a) using the relation  $^{25}$

$$\mu = \frac{\textit{L}}{\textit{CV}_{ds}} \frac{\textit{dI}_{ds}}{\textit{dV}_{gs}}$$

The mobility curves (Figure 3c) show a peak mobility of about 3000 cm²/(V · s) for electrons and about 3300 cm²/V · s for holes for the two adjacent n- and p-type FETs on the same SWCNT. Although the peak mobility for either electron or hole, as shown in Figure 3c, is not the highest mobility reported for SWCNT with similar diameter,  $^{19,24,25}$  this is the first time that high performance is achieved in CMOS circuit simultaneously for both the n-type and p-type FETs. The near-perfect symmetry on the mobility between electron and hole manifests experimentally the intrinsic symmetric band structure of the CNT.

Figure 3. Characteristics of the CNT-based CMOS inverter as shown in Figure 1b. The gate length for both the n- and p-FETs of the CMOS inverter is  $L_g = 4.0 \ \mu m$ . (a) Field transfer characteristic ( $I_{ds} - V_{gs}$ ), (b) output characteristic ( $I_{ds} - V_{ds}$ ), and (c) field-dependent carrier mobility for both the n- and p-type FET devices at low bias of  $V_{ds} = 0.1 \text{ V}$ . (d) Voltage transfer characteristics ( $V_{\text{out}} - V_{\text{in}}$ ), (e) field-dependent voltage gain, and (f) operating current curves ( $I_{\text{leakage}} - V_{\text{in}}$ ) of the inverter under bias of  $V_{\rm dd} = 2.0$  and 1.0 V.

The voltage transfer characteristics of the CNTbased CMOS inverter were measured and shown in Figure 3d for two bias voltages  $V_{\rm dd} = 2.0$  and 1.0 V. Profiting from the symmetric performance between the n-type and p-type FETs, the voltage transfer characteristics exhibit a perfect output "high" or "1" state with  $V_{\rm out} = V_{\rm dd}$  for small input with  $V_{\rm in} < -0.5$  V, and a perfect "low" or "0" state output with Vout down to the ground level of 0 V for both  $V_{\rm dd} = 1.0$  and 2.0 V. For small input or  $V_{qs}$  for both the p- and n-type FETs, the p-FET is open and n-FET is closed, resulting in a very small current ( $\sim$ nA, for  $V_{dd} = 2.0$  V; see Figure 3f) and voltage drop  $V_{\rm ds}$   $\sim$  mV on the p-FET and therefore an almost perfect output with  $V_{\rm out} = V_{\rm dd} - V_{\rm ds} \sim V_{\rm dd}$ . For

large input V<sub>in</sub>, the p-type FET is closed and n-type FET is open, leading to a very small output voltage  $V_{\text{out}} =$  $V_{\sf GND} + V_{\sf ds} \sim {\sf mV}$ , that is, an almost perfect "0" output. In previously published CNT-based inverters, 13-16,26,27 the high level was much smaller than  $V_{\rm dd}$  due to the limited performance of the n-type FETs used, which leads to large standby current and undesired power dissipation. Output transition from "high" state to "low" state starts to occur when the p-FET begins to enter its offstate, that is, when  $V_{\rm qs} \approx V_{\rm in} - V_{\rm dd} \leq V_{\rm th}$  or  $V_{\rm in} \leq V_{\rm dd}$  +  $V_{\rm th}$  for the p-type FET. Therefore, the larger the applied voltage  $V_{\rm dd}$  is, the higher the inverter threshold voltage (at which the output transition occurs) is, and this is clearly demonstrated in Figure 3d, which shows that

the inverter threshold voltage shifts toward smaller value when  $V_{dd}$  decreases from 2.0 to 1.0 V.

The highly symmetric n- and p-FETs result in an extremely sharp transition in the dc voltage transfer characteristic, as shown in Figure 3d, leading to the highest-to-date voltage gain of 160 under the supplied voltage of  $V_{\rm dd} = 2.0$  V and therefore high noise immunity. The voltage gain decreases rapidly with decreasing supplied voltage but remains more than 30 for  $V_{\rm dd} = 1.0$  V, and this is large enough for logical circuit design.

The power dissipated by the IC chip is a very important concern, and in particular the FET off-current leakage is perhaps the greatest problem facing the continued scaling of Si-based CMOS technology. In dc (or standby) operation, the dc power dissipation of the CMOS inverter may be estimated as

$$P_{\rm dc} = V_{\rm dd} (I_{\rm low} + I_{\rm hight})/2 \tag{1}$$

where  $I_{low}$  is the standby current I at  $V_{in} = low$  and  $I_{high}$ at  $V_{\rm in} = \text{high. } I_{\rm low}$  is typically 0.01-2 nA, which rises to about  $I_{high} = 0.03-5$  nA at  $V_{in} = high$  (Figure 3f). The dc operation thus results in  $P_{\rm dc}\sim 0.03$  nW for  $V_{\rm dd}=1$  V and 7 nW for  $V_{dd} = 2$  V. For a large supplied voltage (e.g.,  $V_{dd} = 2 \text{ V}$ ), the invert current increases significantly from the standby value of about 2-5 nA to more than 30 nA at the transition region between -0.4 and 0.1 V. However, when  $V_{\rm dd}$  is lowered to 1.0 V, the peak in the inverter current disappears, and for the full range of input voltage, the current is on the order of tens of pA, which is submerged by the noise signal, as shown in Figure 3f. Huge benefit is thus expected to be gained when we lower the supplied voltage from 2.0 to 1.0 V. While this decrease in  $V_{dd}$  results in about five times reduction in the voltage gain from 160 to about 30, the dc power dissipation of the inverter reduces more than 2 orders of magnitude from about 7 to 0.03 nW. The dynamic operation of the CNT-based CMOS inverter is even more advantageous in supplied voltage scaling. This is because at lower  $V_{dd}$  both n- and p-type FETs are never fully open at the same time, and the short circuit or leakage current (Figure 3f) of the inverter does not show any significant peak or increase in the transition region.

CNT-based CMOS devices are not only more symmetric, operating faster and consuming less power

TABLE 1. Comparison of Main Process Steps between SWCNT-Based and Standard Twin-Well Si CMOS Technology with Shallow Trench Isolation<sup>28</sup> before Interconnection<sup>a</sup>

|                        |             |         | ion          | film   |       |

|------------------------|-------------|---------|--------------|--------|-------|

|                        | lithography | etching | implantation | growth | total |

| Si-CMOS                | 10          | 6       | 8            | 8      | 32    |

| SWCNT CMOS (this work) | 5           | 5       | 0            | 7      | 17    |

The process for fabricating assistant electrodes to select semiconducting SWCNTs is considered in SWCNT CMOS. The etching process includes wet etching, dry ecting, CMP, and lift-off, and the flim growth process includes thermal growth and deposition growth.

than Si-based CMOS devices, but their fabrication is also simpler. We compare the main process steps between CNT-based and standard twin-well Si CMOS technology<sup>28</sup> before an interconnection process in Table 1, showing clearly that the CNT-based CMOS technology is much simpler than that of the Si-based CMOS. This is largely due to the doping-free and isolating-free process we developed for the CNT-based CMOS process. This process also requires fewer steps in other main processes than that of the Si-based CMOS, including fewer lithography, etching, and film growth steps.

#### CONCLUSION

In conclusion, high-performance n-type (Sccontacted) and p-type (Pd-contacted) FETs with selfaligned gates are fabricated on the same SWCNT. This SWCNT-based CMOS technology is much simpler than Si-based CMOS technology due to its doping-free and isolating-free process. Detailed examination of 15 FETs shows that n-type and p-type FETs are almost perfectly symmetric both on dc performance and dynamical operation via gate delay, and this symmetry results from the intrinsic symmetry in the band structures of the CNT. Both n- and p-type CNT FETs are scalable; that is, their performances can be boosted up as the gate length scaling down. The voltage transfer characteristics of the CNT-based CMOS inverter show a perfect "1" (with  $V_{\text{out}} = V_{\text{dd}}$ ) and "0" state (with  $V_{\text{in}} = V_{\text{GND}}$ ) and the highest-to-date voltage gain of over 160. High field carrier mobility is simultaneously realized in the two adjacent n-type FET (3000 cm<sup>2</sup>/V·s) and in p-type FET (3300  $cm^2/V \cdot s$ ), which are fabricated on the same SWCNT in a CMOS inverter.

## **EXPERIMENTAL SECTION**

Ultralong SWCNTs about a few hundred micrometers were directionally grown on a heavily n-doped silicon wafer via a catalytic chemical vapor deposition, and the wafer was covered with a layer of thermally grown SiO<sub>2</sub> (500 nm).<sup>29</sup> The silicon substrate is used as the back gate with the SiO<sub>2</sub> being the gate dielectric, and semiconducting SWCNTs were identified via field-effect measurement using the back gate and then used for following CMOS device and circuit fabrications. p-Type CNT FETs with self-aligned gate structure were fabricated at first. Windows for source and drain electrodes

were first patterned *via* electron beam lithography. Pd film of 80 nm was then deposited by e-beam evaporation followed by lift-off. The gate window was then patterned *via* electron beam lithography, and a 15 nm HfO<sub>2</sub> film with dielectric constant of about 15 was grown by ALD at 90° followed by 10 nm Pd film deposition by e-beam evaporation. The standard lift-off process was then used to form the self-aligned HfO<sub>2</sub>/Pd gate stack to finish the fabrication of p-FETs. <sup>19</sup> n-FETs were fabricated with a process similar to that for p-FETs, but Sc was used instead of Pd as the S, D, and gate electrodes.

Acknowledgment. This work was supported by the Ministry of Science and Technology (Grant Nos. 2006CB932401 and 2006CB932402) and the National Science Foundation of China (Grant No. 90606026).

## **REFERENCES AND NOTES**

- (a) http://en.wikipedia.org/wiki/CMOS. (b) Baker, R. J. CMOS: Circuit Design, Layout, and Simulation, 2nd ed. (Revised);Wiley-IEEE: New York, 2008.

- Passlack, M.; Zurcher, P.; Rajagopalan, K.; Droopad, R.; Abrokwah, J.; Tutt, M.; Park, Y.-B.; Johnson, E.; Hartin, O.; Zlotnicka, A.; et al. High Mobility III-V MOSFETs For RF and Digital Applications. *IEDM* 2007, 621–624.

- Chau, R.; Doyle, B.; Datta, S.; Kavalieros, J.; Zhang, K. Integrated Nanoelectronics for the Future. *Nat. Mater.* 2007, 6, 810–812.

- Natarajan, S.; Armstrong, M.; bost, M.; Brain, R.; Brazier, M.; Chang, C. H.; Chikarmane, V.; Childs, M.; Deshpande, H.; Dev, K.; et al. A 32 nm Logic Technology Featuring 2nd-Generation High-k + Metal-Gate Transistors, Enhanced Channel Strain and 0.171 μm² SRAM Cell Size in a 291 Mb Array. IEDM 2008, 4796777.

- 5. Service, R. F. Is Silicon's Reign Nearing Its End? *Science* **2009**, *323*, 1000–1002.

- Biercuk, M. J.; Ilani, S.; Marcus, C. M.; McEuen, P. L. Electrical Transport in Single-Wall Carbon Nanotubes. *Carbon Nanotubes* 2008, 111, 455–493.

- Dai, H. J.; Javey, A.; Pop, E.; Mann, D.; Lu, Y. Electrical Transport Properties and Field-Effect Transistors of Carbon nanotube. NANO: Brief Reports and Reviews 2006, 1, 1–13.

- 8. Avouris, Ph.; Chen, Z. H.; Perebeinos, V. Carbon-Based Electronics. *Nat. Nanotechnol.* **2007**, *2*, 605–615.

- Saito, R.; Dresselhaus, G.; Dresselhaus, M. S. *Physical Properties of Carbon Nanotubes*; World Scientific Publishing Company: River Edge, NJ, 1998; pp 59–65.

- Javey, A.; Guo, J.; Wang, Q.; Lundstrom, M.; Dai, H. J. Ballistic Carbon Nanotube Field-Effect Transistor. *Nature* 2003, 424, 654–657.

- Javey, A.; Guo, J.; Farmer, D. B.; Wang, Q.; Wang, D. W.; Gordon, R. G.; Lundstrom, M.; Dai, H. J. Carbon Nanotube Field-Effect Transistors with Integrated Ohmic Contacts and High-k Gate Dielectrics. Nano Lett. 2004, 4, 447–450.

- Javey, A.; Kim, H.; Brink, M.; Wang, Q.; Ural, A.; Guo, J.; Mcintyre, P.; McEuen, P.; Lundstrom, M.; Dai, H. J. High-κ Dielectrics for Advanced Carbon-Nanotube Transistors and Logic Gates. *Nat. Mater.* 2002, 1, 241–246.

- Javey, A.; Wang, Q.; Ural, A.; Li, Y. M.; Dai, H. J. Carbon Nanotube Transistor Arrays For Multistage Complementary Logic and Ring Oscillators. *Nano Lett.* 2002, 2, 929–932.

- Liu, X. L.; Lee, C. H.; Zhou, C. W. Carbon Nanotube Field-Effect Inverters. Appl. Phys. Lett. 2001, 79, 3329–3331.

- Derycke, V.; Martel, R.; Appenzeller, J.; Avouris, Ph. Carbon Nanotube Inter- and Intramolecular Logic Gates. *Nano Lett.* 2001, 1, 453–456.

- Chen, Z. H.; Appenzeller, Z. H.; Lin, Y. M.; Sippel-Oakley, J.; Rinzler, A. G.; Tang, J. Y.; Wind, S. J.; Solomon, P. M.; Avouris, Ph. An Integrated Logic Circuit Assembled on a Single Carbon Nanotube. Science 2006, 311, 1735.

- Zhang, Z. Y.; Liang, X. L.; Wang, S.; Yao, K.; Hu, Y. F.; Zhu, Y. Z.; Chen, Q.; Zhou, W. W.; Li, Y.; Yao, Y. G.; et al. Doping-Free Fabrication of Carbon Nanotube Based Ballistic CMOS Devices and Circuits. *Nano Lett.* 2007, 7, 3603–3607.

- Zhang, Z. Y.; Wang, S.; Ding, L.; Liang, X. L.; Xu, H. L.; Shen, J.; Chen, Q.; Cui, R. L.; Li, Y.; Peng, L. M. High-Performance n-Type Carbon Nanotube Field-Effect Transistors with Estimated Sub-10-ps Gate Delay. Appl. Phys. Lett. 2008, 92, 133117

- Zhang, Z. Y.; Wang, S.; Ding, L.; Liang, X. L.; Pei, T.; Shen, J.;

Xu, H. L.; Chen, Q.; Cui, R. L.; Li, Y.; et al. Self-Aligned

Ballistic n-Type Single-Walled Carbon Nanotube Field-Effect Transistors with Adjustable Threshold Voltage. *Nano Lett.* 2008, 8, 3696–3701.

- Wang, S.; Zhang, Z. Y.; Ding, L.; Liang, X. L.; Shen, J.; Xu, H. L.; Chen, Q.; Cui, R. L.; Li, Y.; Peng, L. M. A Doping-Free Carbon Nanotube CMOS Inverter-Based Bipolar Diode and Ambipolar Transistor. Adv. Mater. 2008, 20, 3258–3262.

- Chau, R.; Datta, S.; Doczy, M.; Jin, B.; Kavalieros, J.; Majumdar, A.; Metz, M.; Radosavljevic, M. Benchmarking Nanotechnology for High-Performance and Low-Power Logic Transistor Applications. *IEEE Trans. Nanotechnol.* 2005, 4, 153–158.

- Lin, Y. M.; Appenzeller, J.; Knoch, J.; Chen, Z. H.; Avouris, Ph. Low-Frequency Current Fluctuations in Individual Semiconducting Single-Wall Carbon Nanotubes. *Nano Lett.* 2006. 6, 930–936.

- 23. Sze, S. M., *Physics of Semiconductor Devices*; Wiley: New York, 1981; pp 29–30.

- Zhou, X. J.; Park, J. Y.; Huang, S. M.; Liu, J.; McEuen, P. L. Band Structure, Phonon Scattering, and the Performance Limit of Single-Walled Carbon Nanotube Transistor. *Phys. Rev. Lett.* **2005**, *95*, 146805.

- Drkop, T.; Getty, S. A.; Cobas, E.; Fuhrer, M. S. Extraordinary Mobility in Semiconducting Carbon Nanotubes. *Nano Lett.* 2004. 4, 35–39.

- Cao, Q.; Kim, H.; Pimparkar, N.; Kulkarni, J. P.; Wang, C. J.; Shim, M.; Roy, K.; Alam, M. A.; Rogers, J. A. Medium-Scale Carbon Nanotube Thin-Film Integrated Circuits on Flexible Plastic Substrates. *Nature* **2008**, *454*, 495–500.

- Ryu, K. M.; Badmaev, A.; Wang, C.; Lin, A.; Patil, N.; Gomez, L.; Kumar, A.; Mitra, S.; Wong, H.-S.; Zhou, C. W. CMOS-Analogous Wafer-Scale Nanotube-on-Insulator Approach for Submicrometer Devices and Integrated Circuits Using Aligned Nanotubes. *Nano Lett.* **2009**, *9*, 189–197.

- 28. Plummer, J. D.; Deal, M. D.; Griffin, P. B. *Silicon VLSI Technology: Fundamentals, Practice and Modeling*; Prentice Hall: New York, 2000; pp 51–82.

- Zhou, W. W.; Han, Z. Y.; Wang, J. Y.; Zhang, Y.; Jin, Z.; Sun, X.; Zhang, Y. W.; Yan, C. H.; Li, Y. Copper Catalyzing Growth of Single-Walled Carbon Nanotubes on Substrates. *Nano Lett.* 2006, 6, 2987–2990.